# WINSTAR Display

# **OLED SPECIFICATION**

Model No:

WEO002004C

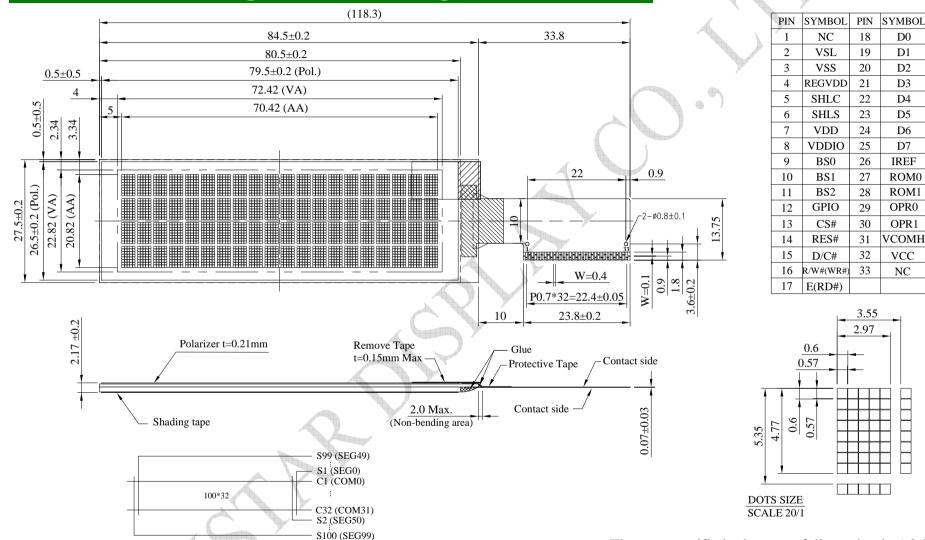

## **General Specification**

| Item                 | Dimension               | Unit |

|----------------------|-------------------------|------|

| Number of Characters | 20 Characters x 4 Lines | -    |

| Module dimension     | 84.5 x 27.5 x 2.17      | mm   |

| View area            | 72.42 x 22.82           | mm   |

| Active area          | 70.42 x 20.82           | mm   |

| Dot size             | 0.57 x 0.57             | mm   |

| Dot pitch            | 0.60 x 0.60             | mm   |

| Character size       | 2.97 x 4.77             | mm   |

| Character pitch      | 3.55 x 5.35             | mm   |

| LCD type             | OLED , Monochrome       |      |

| Duty                 | 1/32                    |      |

| IC                   | SSD1311                 |      |

| Interface            | 6800,8080,SPI,I2C       |      |

| Size                 | 2.89 inch               |      |

#### **Contour Drawing & Block Diagram**

### **Interface Pin Function**

| Pin No. | Symbol | Pin Type | Description                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | NC     | _        | To connection                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 2       | VSL    | P        | This is segment voltage (output low level) reference pin.  When external VSL is not used, this pin should be left open.  When external VSL is used, connect with resistor and diode to round (details depend on application).                                                                                                                   |  |  |  |  |  |

| 3       | VSS    | P        | Ground pin. It must be connected to external ground.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 4       | REGVDD | I        | nternal VDD regulator selection pin in 5V I/O application mode. When this pin is pulled HIGH, internal VDD regulator is enabled 5V I/O application). When this pin is pulled LOW, internal VDD regulator is disabled Low voltage I/O application).                                                                                              |  |  |  |  |  |

| 5       | SHLC   | I        | This pin is used to determine the Common output scanning direction.  COM scan direction  SHLC   COM scan direction  1   COM0 to COM31   (Normal)  0   COM31 to COM0   (Reverse)  Note  (1) 0 is connected to VSS  (2) 1 is connected to VDDIO                                                                                                   |  |  |  |  |  |

| 6       | SHLS   | I        | This pin is used to change the mapping between the display data column address and the Segment driver.  SEG scan direction  SHLS  SEG direction  1  SEG0 to SEG99 (Normal)  0  SEG99 to SEG0 (Reverse)  Note  (1) 0 is connected to VSS  (2) 1 is connected to VDDIO                                                                            |  |  |  |  |  |

| 7       | VDD    | Р        | Power supply for core logic operation. VDD can be supplied externally or regulated internally. In LV IO application (internal VDD is disabled), this is a power input pin. In 5V IO application (internal VDD is enabled), VDD is regulated internally from VDDIO. A capacitor should be connected between VDD and VSS under all circumstances. |  |  |  |  |  |

| 8       | VDDIO  | P        | Low voltage power supply and power supply for interface logic level in both Low Voltage I/O and 5V I/O application. It should match with the MCU interface voltage level and must be connected to external source.                                                                                                                              |  |  |  |  |  |

| 9       | BS0    | I        | MCU bus interface selection pins. Select appropriate logic                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 10 | DC1         |      | 1 '1 1' 1 C 11 ' . 11 DGO DG1 1DGO                                                       |  |  |  |  |  |

|----|-------------|------|------------------------------------------------------------------------------------------|--|--|--|--|--|

| 10 | BS1         |      | setting as described in the following table. BS2, BS1 and BS0 are                        |  |  |  |  |  |

| 11 | BS2         |      | pin select.                                                                              |  |  |  |  |  |

| 11 | <b>D</b> 52 |      | Bus Interface selection                                                                  |  |  |  |  |  |

|    |             |      | BS[2:0] Interface                                                                        |  |  |  |  |  |

|    |             |      | 000 Serial Interface                                                                     |  |  |  |  |  |

|    |             |      | 001 Invalid                                                                              |  |  |  |  |  |

|    |             |      | 010 I <sup>2</sup> C                                                                     |  |  |  |  |  |

|    |             |      | 011 Invalid                                                                              |  |  |  |  |  |

|    |             |      | 100 8-bit 6800 parallel                                                                  |  |  |  |  |  |

|    |             |      | 101 4-bit 6800 parallel                                                                  |  |  |  |  |  |

|    |             |      | 110 8-bit 8080 parallel                                                                  |  |  |  |  |  |

|    |             |      | 111 4-bit 8080 parallel                                                                  |  |  |  |  |  |

|    |             |      | Note                                                                                     |  |  |  |  |  |

|    |             |      | (1) 0 is connected to VSS                                                                |  |  |  |  |  |

|    |             |      | (2) 1 is connected to VDDIO                                                              |  |  |  |  |  |

| 12 | GPIO        | I/O  | It is a GPIO pin. Details refer to OLED command DCh.                                     |  |  |  |  |  |

|    |             | 1/ 0 | -                                                                                        |  |  |  |  |  |

| 13 | CS#         | I    | This pin is the chip select input connecting to the MCU.                                 |  |  |  |  |  |

|    |             |      | The chip is enabled for MCU communication only when CS# is                               |  |  |  |  |  |

|    |             |      | pulled LOW (active LOW).                                                                 |  |  |  |  |  |

|    |             |      | In I2C mode, this pin must be connected to VSS.                                          |  |  |  |  |  |

| 14 | RES#        | I    | This pin is reset signal input.                                                          |  |  |  |  |  |

|    | TCLS!!      | -    | When the pin is pulled LOW, initialization of the chip is executed.                      |  |  |  |  |  |

|    |             |      | Keep this pin pull HIGH during normal operation.                                         |  |  |  |  |  |

| 15 | D/C#        | I    | This pin is Data/Command control pin connecting to the MCU.                              |  |  |  |  |  |

| 13 | D/Cπ        | 1    | 1                                                                                        |  |  |  |  |  |

|    |             |      | When the pin is pulled HIGH, the data at D[7:0] will be                                  |  |  |  |  |  |

|    |             |      | interpreted as data.                                                                     |  |  |  |  |  |

|    |             |      | When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register |  |  |  |  |  |

|    |             |      | to a command register.                                                                   |  |  |  |  |  |

|    |             |      | In I2C mode, this pin acts as SA0 for slave address selection.                           |  |  |  |  |  |

|    |             |      | When serial interface is selected, this pin must be connected to                         |  |  |  |  |  |

|    |             |      | VSS.                                                                                     |  |  |  |  |  |

| 16 | R/W#(WR#)   | T    | This pin is read / write control input pin connecting to the MCU                         |  |  |  |  |  |

|    |             |      | interface.                                                                               |  |  |  |  |  |

|    |             |      | When 6800 interface mode is selected, this pin will be used as                           |  |  |  |  |  |

|    |             | 7    | Read/Write (R/W#) selection input. Read mode will be carried out                         |  |  |  |  |  |

|    |             | 7    | when this pin is pulled HIGH and write mode when LOW.                                    |  |  |  |  |  |

|    |             |      |                                                                                          |  |  |  |  |  |

|    |             |      | When 8080 interface mode is selected, this pin will be the Write                         |  |  |  |  |  |

| 4  |             |      | (WR#) input. Data write operation is initiated when this pin is                          |  |  |  |  |  |

|    |             |      | pulled LOW and the chip is selected.                                                     |  |  |  |  |  |

|    |             |      | When serial or I2C interface is selected, this pin must be                               |  |  |  |  |  |

| A  |             |      | connected to VSS.                                                                        |  |  |  |  |  |

|          |                | _         |                                                                     |  |  |  |  |  |

|----------|----------------|-----------|---------------------------------------------------------------------|--|--|--|--|--|

| 17       | E(RD#)         | I         | This pin is MCU interface input.                                    |  |  |  |  |  |

|          |                |           | When 6800 interface mode is selected, this pin will be used as the  |  |  |  |  |  |

|          |                |           | Enable (E) signal.                                                  |  |  |  |  |  |

|          |                |           | Read/write operation is initiated when this pin is pulled HIGH and  |  |  |  |  |  |

|          |                |           | the chip is selected.                                               |  |  |  |  |  |

|          |                |           | When 8080 interface mode is selected, this pin receives the Read    |  |  |  |  |  |

|          |                |           | (RD#) signal. Read operation is initiated when this pin is pulled   |  |  |  |  |  |

|          |                |           | LOW and the chip is selected.                                       |  |  |  |  |  |

|          |                |           | When serial or I2C interface is selected, this pin must be          |  |  |  |  |  |

|          |                |           | connected to VSS.                                                   |  |  |  |  |  |

| 18       | D0             | I/O       | These pins are bi-directional data bus connecting to the MCU data   |  |  |  |  |  |

|          |                | 2, 0      | bus.                                                                |  |  |  |  |  |

| 19       | D1             |           | Unused pins are recommended to tie LOW.                             |  |  |  |  |  |

| 20       | D2             |           | When serial interface mode is selected, D0 will be the serial clock |  |  |  |  |  |

| 20       | D2             |           | input: SCLK; D1 will be the serial data input: SID and D2 will be   |  |  |  |  |  |

| 21       | D3             |           | the serial data output: SOD.                                        |  |  |  |  |  |

| 22       | D.4            |           | When I2C mode is selected, D2, D1 should be tied together and       |  |  |  |  |  |

| 22       | D4             |           | serve as SDAout, SDAin in application and D0 is the serial clock    |  |  |  |  |  |

| 23       | D5             |           | input, SCL.                                                         |  |  |  |  |  |

|          |                |           | input, SCL.                                                         |  |  |  |  |  |

| 24       | D6             |           |                                                                     |  |  |  |  |  |

| 25       | D7             |           |                                                                     |  |  |  |  |  |

|          |                |           |                                                                     |  |  |  |  |  |

| 26       | IREF           | I         | This pin is the segment output current reference pin.               |  |  |  |  |  |

|          |                |           | IREF is supplied externally.                                        |  |  |  |  |  |

|          |                |           | A resistor should be connected between this pin and VSS to          |  |  |  |  |  |

|          |                |           | maintain current of around 15uA.                                    |  |  |  |  |  |

| 27       | ROM0           | I         | These pins are used to select Character ROM; select appropriate     |  |  |  |  |  |

| 20       | DOM1           |           | logic setting as described in the following table. ROM1 and         |  |  |  |  |  |

| 28       | ROM1           |           | ROM0 are pin select as shown in below table:                        |  |  |  |  |  |

|          |                |           | Character ROM selection                                             |  |  |  |  |  |

|          |                |           | ROM1 ROM0 ROM                                                       |  |  |  |  |  |

|          |                |           | 0 0 A                                                               |  |  |  |  |  |

|          |                |           | 0 I B                                                               |  |  |  |  |  |

|          | And the second |           | 1 0 C                                                               |  |  |  |  |  |

|          |                |           | 1 I S/W selectable (3)                                              |  |  |  |  |  |

|          |                |           | Note                                                                |  |  |  |  |  |

|          |                | <i>JP</i> | (1) 0 is connected to VSS                                           |  |  |  |  |  |

|          | 7              |           | (2) 1 is connected to VDDIO                                         |  |  |  |  |  |

| 29       | OPR0           | I         | This pin is used to select the character number of character        |  |  |  |  |  |

| All      |                |           | generator.                                                          |  |  |  |  |  |

| 30       | OPR1           |           | Character RAM selection                                             |  |  |  |  |  |

|          | ~              |           | OPRI OPRO CGROM CGRAM                                               |  |  |  |  |  |

| <b>√</b> |                |           | 1 1 256 0                                                           |  |  |  |  |  |

|          |                |           | 0 1 248 8                                                           |  |  |  |  |  |

|          |                |           | 1 0 250 6                                                           |  |  |  |  |  |

|          |                |           | 0 0 240 8                                                           |  |  |  |  |  |

|          |                |           | Note                                                                |  |  |  |  |  |

|          |                |           | (1) 0 is connected to VSS                                           |  |  |  |  |  |

|          |                |           | (2) 1 is connected to VDDIO                                         |  |  |  |  |  |

| 1        | 1              | 1         | (4) 1 is connected to VDDIO                                         |  |  |  |  |  |

| 31 | VCOMH | P | COM signal deselected voltage level.                                                                                                             |  |  |

|----|-------|---|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    |       |   | A capacitor should be connected between this pin and VSS.                                                                                        |  |  |

|    |       |   | No external power supply is allowed to connect to this pin.                                                                                      |  |  |

| 32 | VCC   | Р | Power supply for panel driving voltage. This is also the most positive power voltage supply pin. It is supplied by external high voltage source. |  |  |

| 33 | NC    | _ | No connection                                                                                                                                    |  |  |

### **Absolute Maximum Ratings**

| Item                      | Symbol | Min  | Max   | Unit |

|---------------------------|--------|------|-------|------|

| Supply Voltage For Logic  | VDD    | -0.3 | VDDIO | V    |

| Power Supply for I/O pins | VDDIO  | -0.3 | 6     | V    |

| Operating Voltage         | VCC    | 0    | 16    | V    |

| Operating Temperature     | TOP    | -40  | +80   | °C   |

| Storage Temperature       | TST    | -40  | +85   | °C   |

### **Electrical Characteristics**

#### **DC Electrical Characteristics**

| Item                                 | Symbol | Condition                 | Min       | Тур  | Max       | Unit |

|--------------------------------------|--------|---------------------------|-----------|------|-----------|------|

| Supply Voltage For Logic             | VDD    | Low Voltage I/O           | 2.8       | 3.0  | 3.3       | V    |

|                                      |        | 5V I/O<br>(VDD as output) | _         | _    | _         | V    |

| Power cumply for I/O pine            | VDDIO  | Low Voltage I/O           | 2.8       | 3.0  | 3.3       | V    |

| Power supply for I/O pins            |        | 5V I/O                    | 4.8       | 5.0  | 5.3       | V    |

| Operating Voltage                    | VCC    | _                         | 9.5       | 10.0 | 10.5      | V    |

| Input High Volt.                     | VIH    | _                         | 0.8xVDDIO | _    | _         | V    |

| Input Low Volt.                      | VIL    | _                         | _         | _    | 0.2xVDDIO | V    |

| Output High Volt.                    | VOH    | IOH=-0.5mA                | 0.9xVDDIO | _    | _         | V    |

| Output Low Volt.                     | VOL    | IOL=0.5mA                 | _         | _    | 0.1xVDDIO | V    |

| 50% Check Board<br>Operating Current | ICC    | VCC=10V                   | _         | 19   | 21        | mA   |